Nowadays, Machine Learning is commonly integrated into most daily life applications in various fields. The K Nearest Neighbor (KNN), which is a robust Machine Learning algorithm, is traditionally used in classification tasks for its simplicity and training-less nature. Hardware accelerators such as FPGAs and ASICs are greatly needed to meet the increased requirements of performance for these applications. It is well known that ASICs are non-programmable and only fabricated once with high expenses, this makes the fabrication of a complete chip for a specific classification problem inefficient

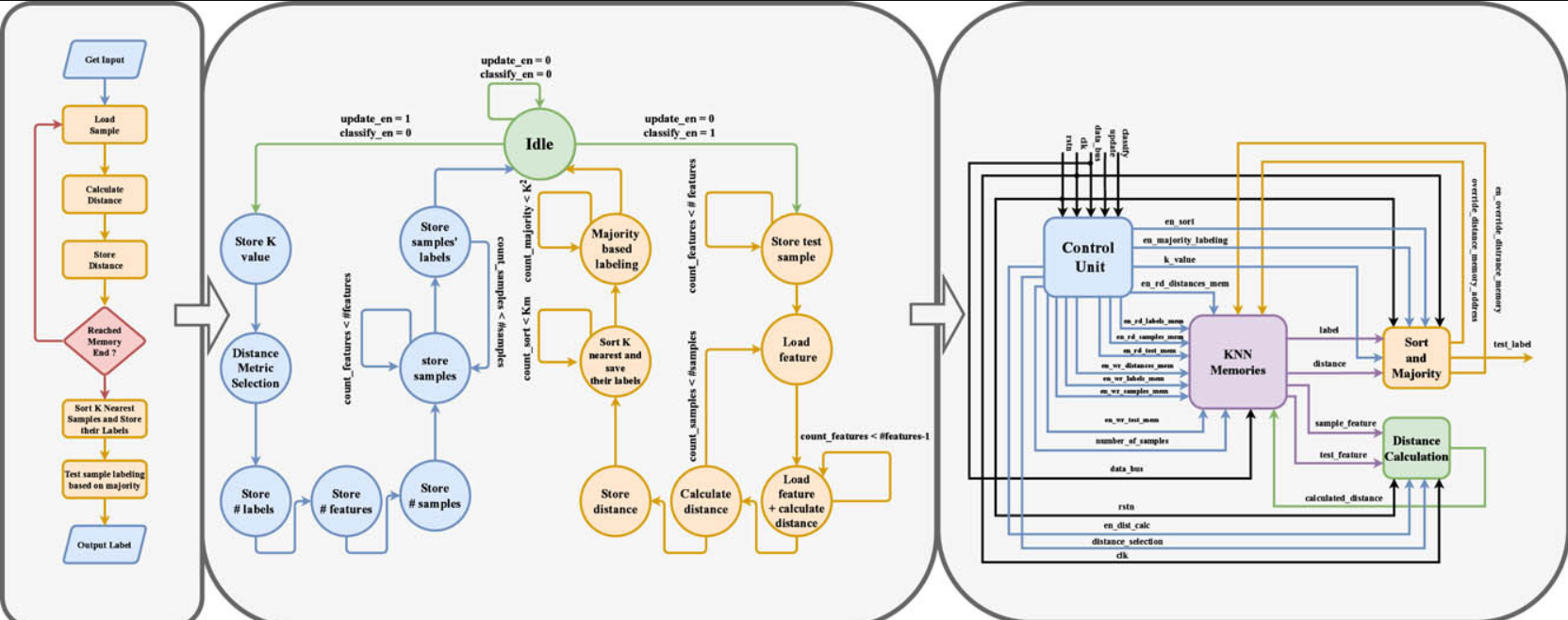

K Nearest Neighbors (KNN) algorithm is a straight-forward yet powerful Machine Learning (ML) tool widely used in classification, clustering, and regression applications. In this work, KNN is applied, with three distance metrics, to classify different datasets, experimentally testing each distance metric effect on the classification performance. A static K is applied for the whole dataset optimally chosen based on a 5-fold cross-validation. A reconfigurable hardware realization on field programmable gate array (FPGA) of each distance metric applying selection sort algorithm is proposed. The

This work is a review article that sheds light on the active and passive sensitivities of the active RC filters based on opamp. This work provides a detailed analysis through different filters realization criteria and sensitivity summary tables and quantitative insight by discussing the most significant. However, some are almost forgotten, filters families in the literature over decades. A detailed mathematical analysis for the passive sensitivity to compare the filters’ realizations is presented. The concept of dealing between filter design theory and filter design circuit realization is

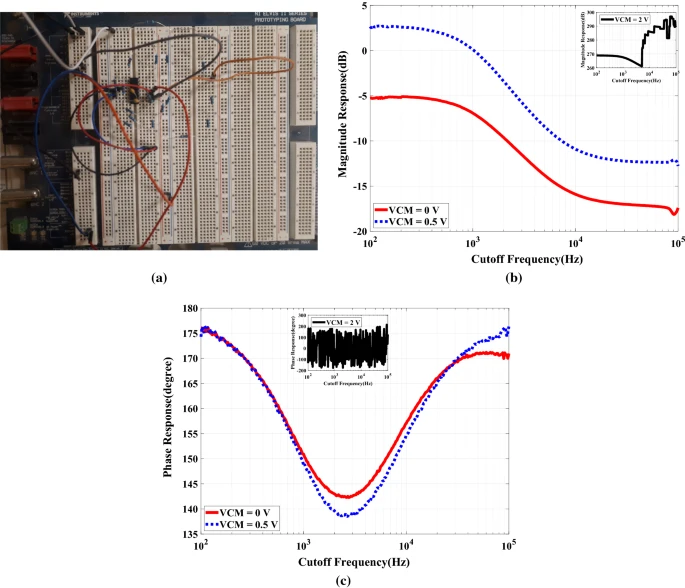

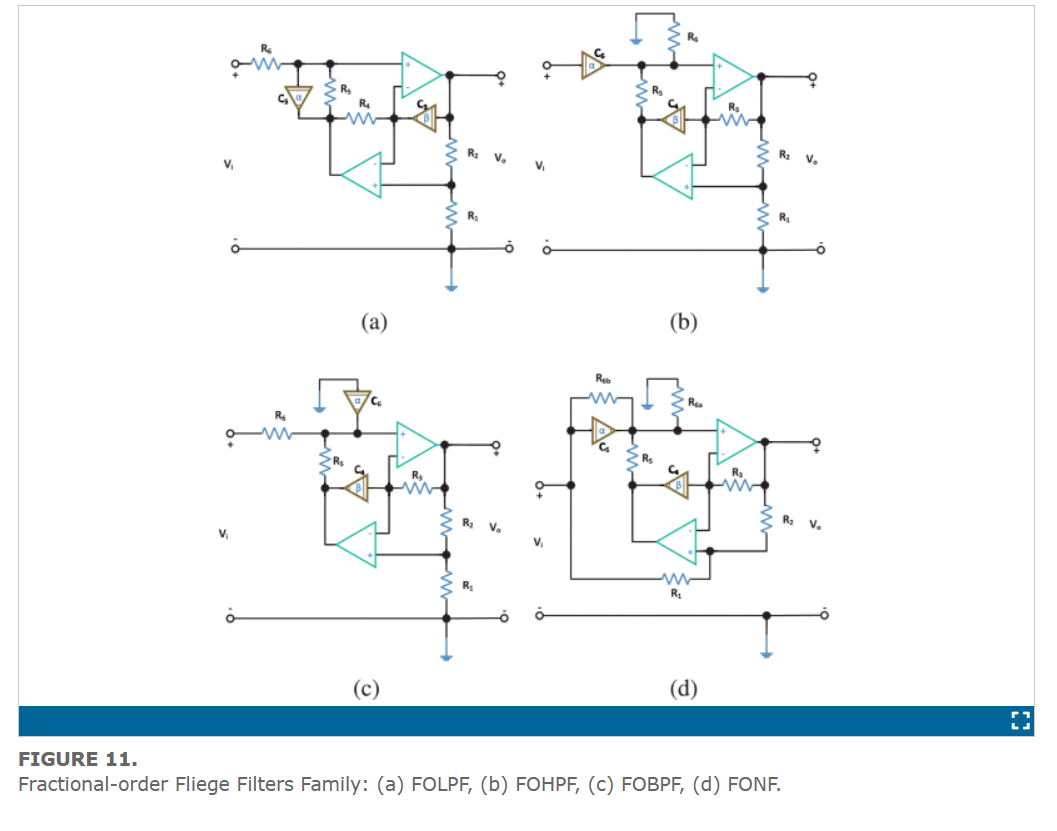

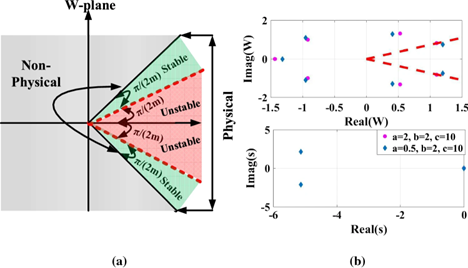

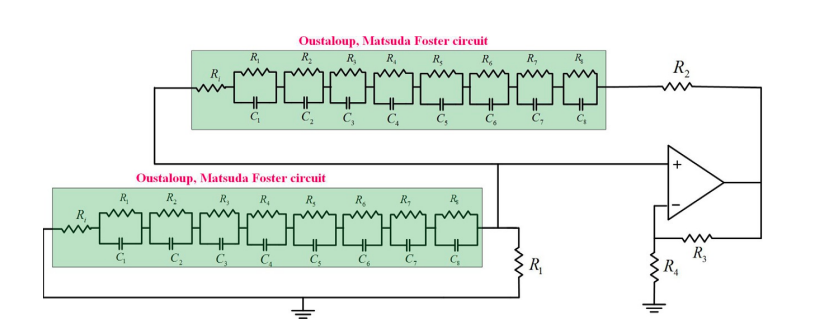

This work explicitly states the design flows of the fractional-order analog filters used by researchers throughout the literature. Two main flows are studied: the FPAA implementation and the circuit realization. Partial-fraction expansion representation is used to prepare the approximated fractional-order response for implementation on FPAA. The generalization of the second-order active RC analog filters based on opamp from the integer-order domain to the fractional-order domain is presented. The generalization is studied from both mathematical and circuit realization points of view. It is

This paper studies the capability of digital architecture to mimic fractal behavior. As chaotic attractors realized digitally had opened many tracks, digital designs mimicking fractals may ultimately achieve the same. This study is based on a complex single-dimensional discrete chaotic system known as the generalized positive logistic map. The fractals realized from this system are linked to the results of the mathematical analysis to understand the fractal behavior with different variations. A digital hardware architecture manifesting the fractal behavior is achieved on FPGA, showing a

Unfortunately, in the original version of the article some typos occurred. The typos have been corrected with this erratum. Below are the corrections:(Formula presented.). © 2019, Springer Science+Business Media, LLC, part of Springer Nature.

This paper presents a secured highly sensitive image encryption system suitable for biomedical applications. The pseudo random number generator of the presented system is based on two discrete logistic maps. The employed maps are: the one dimensional double humped logistic map as well as the two-dimensional delayed logistic map. Different analyses are introduced to measure the performance of the proposed encryption system such as: histogram analysis, correlation coefficients, MAE, NPCR as well as UACI measurements. The encryption system is proven to be highly sensitive to ±0.001% perturbation

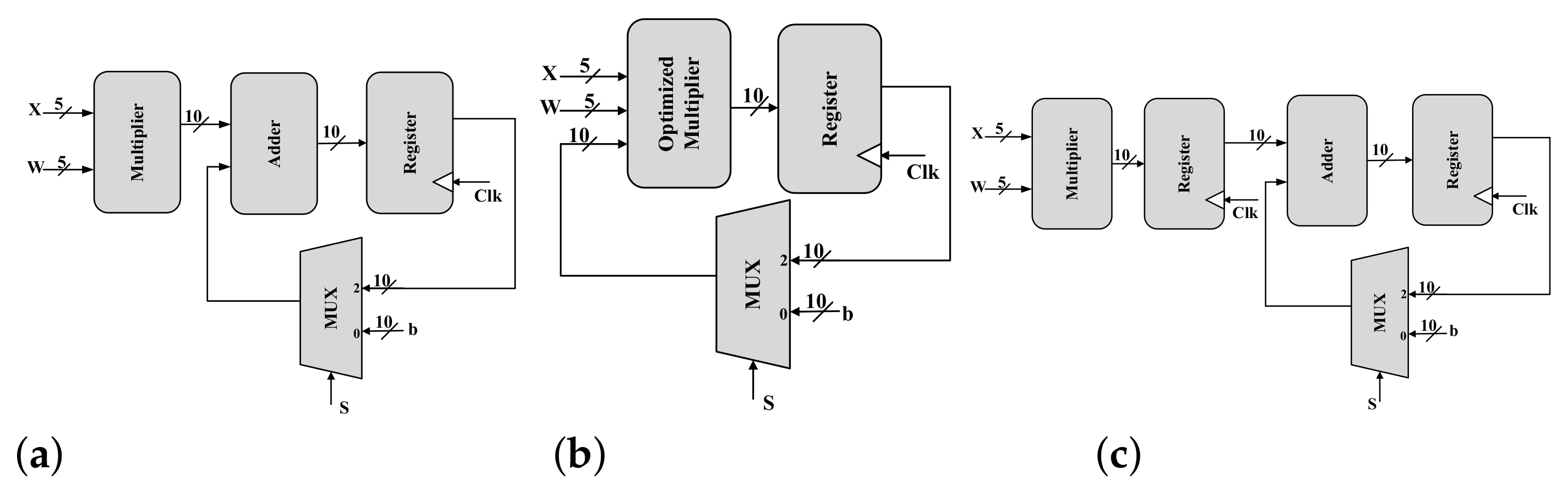

Multiply-Accumulate (MAC) is one of the most commonly used operations in modern computing systems due to its use in matrix multiplication, signal processing, and in new applications such as machine learning and deep neural networks. Ternary number system offers higher information processing within the same number of digits when compared to binary systems. In this paper, a MAC is proposed using a CNTFET-based ternary logic number. Specifically, we build a 5-trit multiplier and 10-trit adder as building blocks of two ternary MAC unit designs. The first is a basic MAC which has two methods to

Despite the complex nature of fractional calculus, it is still fairly possible to reduce this complexity by using integer-order approximation. Each integer-order approximation has its own trade-offs from the complexity, sensitivity, and accuracy points of view. In this chapter, two different fractional-order electronic circuits are studied: the Wien oscillator and the CCII-based KHN filter with two different fractional elements of orders α and β. The investigation is concerned with changes in the response of these two circuits under two approximations: Oustaloup and Matsuda. A detailed review

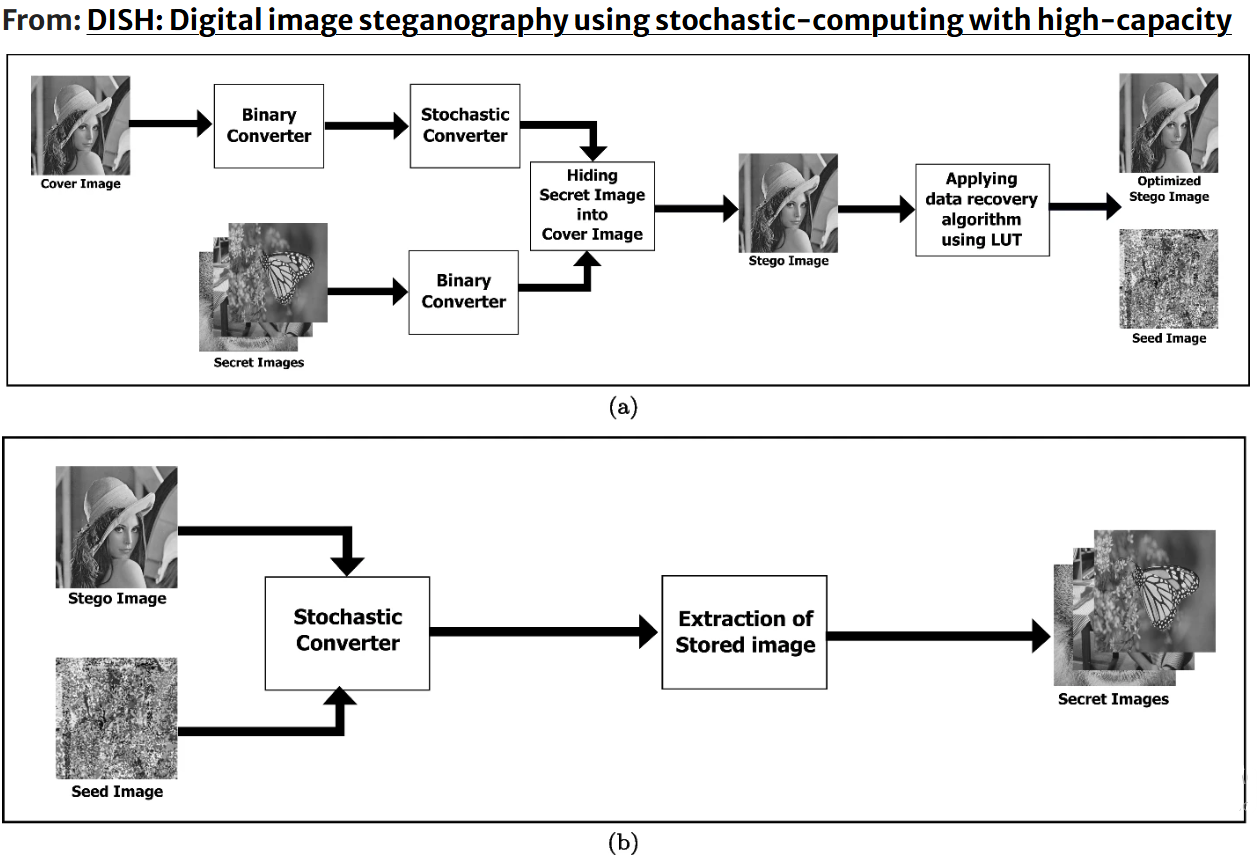

Stochastic computing is a relatively new approach to computing that has gained interest in recent years due to its potential for low-power and high-noise environments. It is a method of computing that uses probability to represent and manipulate data, therefore it has applications in areas such as signal processing, machine learning, and cryptography. Stochastic steganography involves hiding a message within a cover image using a statistical model. Unlike traditional steganography techniques that use deterministic algorithms to embed the message, stochastic steganography uses a probabilistic